CBM-Bus

Der CBM-Bus ist ein von Commodore für seine Heimcomputer-Serie entwickelter serieller Bus.

Er ist eine proprietäre serielle Variante des IEEE-488-Busses und dient zum Anschließen von Peripheriegeräten (hauptsächlich Diskettenlaufwerke und Drucker).[1] Der Bus fand sich in den 6502-basierten Commodore-Heimcomputern vom VC 20 bis zum C128, während die professionellen PET/CBM-Rechner den genormten parallelen IEEE-488-Bus verwendeten. Die Rechner der Commodore-Amiga-Serie verwendeten keine derartige Schnittstelle, stattdessen kamen Anschlüsse für externe Diskettenlaufwerke, ein Parallelport ähnlich dem in IBM-kompatiblen PCs und bei größeren bzw. schnelleren Modellen (A3000 und A4000T) der SCSI-Bus zum Einsatz.

Der CBM-Bus wurde in der Literatur der 1980er Jahre oft auch als (serieller) IEC-Bus bezeichnet. Dies ist aber nicht korrekt, da der CBM-Bus nicht durch die International Electrotechnical Commission standardisiert wurde.

Merkmale

Im Unterschied zum amerikanischen IEEE-488-Standard oder dem internationalen IEC-625-Standard erfolgt die Datenübertragung beim CBM-Bus seriell. Hierzu wird für die Bitübertragung eine Daten- und eine Taktleitung verwendet.[2] Beim C128 in Verbindung mit den Diskettenlaufwerken VC1570, VC1571 und VC1581 kommt zur Bitübertragung eine weitere, schnellere Taktleitung hinzu.[3] Alle Leitungen werden über Open-Drain-Ausgänge angesteuert, die jeweils über einen 1-kΩ-Pull-up-Widerstand mit dem 5-V-Potenzial verbunden sind.[4][5] Insgesamt werden so weniger Signalleitungen erforderlich, was Einsparungen sowohl bei den Ein-/Ausgabe-Chips als auch an den Kabeln und den zugehörigen Steckverbindern möglich machte. Zusätzlich werden beim CBM-Bus einige Ereignisse, für die im IEEE-488-Standard eigene Steuerleitungen vorgesehen sind, über die Daten- und Taktleitung übertragen. Letztlich werden somit nur höchstens 5 statt der 24 Leitungen des IEEE-488-Standardsteckers gebraucht.[6] Das Busprotokoll ist dennoch bei beiden Bussen sehr ähnlich.[7]

Der Computer steuert alle Geräte am CBM-Bus, wozu er die bis zu zwei Byte langen Befehle TALK, LISTEN, UNTALK und UNLISTEN sendet während die /ATN-Leitung einen niedrigen Pegel aufweist.[1][8] Letzteres bedeutet, dass Befehlsbytes und keine Nutzdaten übertragen werden. TALK bzw. LISTEN weist ein Gerät an, Daten zu senden bzw. zu empfangen. UNTALK bzw. UNLISTEN wiederum stoppt das Senden bzw. Empfangen von Nutzdaten bei allen Geräten.

Jedes Gerät besitzt mindestens eine 5 Bit lange Adresse. Die Befehle TALK und LISTEN beinhalten eine solche, womit sie ein Gerät am CBM-Bus ansprechen. Optional kann nach dem ersten Byte des TALK- oder LISTEN-Befehls noch ein dazugehöriges zweites Byte gesendet werden, das eine 5 Bit lange sekundäre Adresse enthält. Die Interpretation der sekundären Adresse ist geräteabhängig, bspw. können damit gewisse Gerätefunktionen ausgewählt und gesteuert werden.[1]

Nachdem mit einem TALK-Befehl ein Sender bzw. mit einem oder mehreren LISTEN-Befehlen ein oder mehrere Empfänger ausgewählt wurden (der Computer spricht sich über den CBM-Bus nicht selbst an), erfolgt die Übertragung der Daten. Hierbei hat die /ATN-Leitung einen hohen Pegel. Das Ende einer Datenübertragung wird durch das Signalisieren von EOI (End Or Identify) vor der Übertragung des letzten Datenbytes angezeigt (außer beim Burstmodus), woraufhin der Computer durch Senden des Befehls UNTALK bzw. UNLISTEN den Sender bzw. alle Empfänger am CBM-Bus deaktiviert.[8]

Anzahl der nutzbaren Geräte

Theoretisch können bis zu 31 Geräte gleichzeitig an den Bus angeschlossen und adressiert werden (wobei jedes Gerät physikalisch ab dem zweiten kettenartig an das jeweils vorherige angeschlossen wird), das Betriebssystem stellte davon 27 Geräteadressen (4 bis 30; 31 ist für UNTALK und UNLISTEN reserviert) zur Verfügung.[1] Praktisch lag die Obergrenze jedoch bei etwa 8 Geräten, was sich aus der maximalen Stromstärke der mit dem Bus verbundenen Ausgangstreiber zum Senden und der Eingangskapazität der ebenfalls mit dem Bus verbundenen Eingangspuffer zum Empfangen ergab. Diese Obergrenze war üblicherweise völlig ausreichend.

Vorgesehen waren die Adressen 4 und 5 für Drucker, 6 für Plotter und 8 bis 11 für Diskettenlaufwerke.[9] Diese Zuordnung war dem Computer jedoch nicht bekannt; demnach war es etwa möglich, den Computer anzuweisen, ein Programm auf den Drucker zu „speichern“, was zum Ausdruck von „Zeichensalat“ führte.

Die Geräteadressen 0 bis 3 waren für „unintelligente“ Peripheriegeräte ohne eigene CPU reserviert, die nicht über den CBM-Bus angeschlossen wurden: 0 für die Tastatur, 1 für die Datasette, 2 für Modems und andere gemäß RS-232 angeschlossene Geräte und 3 für den Bildschirm.[9] Das Betriebssystem sendete daher diese Gerätenummern nicht über den Bus, sondern verwendete die jeweiligen speziellen Zugriffsroutinen, wenn die üblichen Datei-Eingabe-/Ausgabe-Funktionen verwendet wurden. Für Programmierer, die direkt die Zugriffsroutinen für die Ansteuerung des seriellen Busses verwendeten, war es aber auch möglich, Geräte mit den Adressen 0 bis 3 am seriellen Bus anzusprechen.[10]

Anschluss

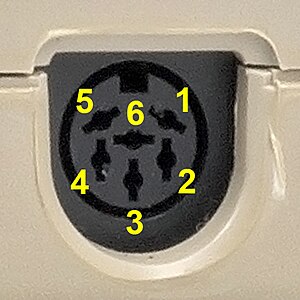

| Pin | Name | Function |

|---|---|---|

| 1 | /SRQIN | Service-Request-Eingang für Peripherie-Anfrage an Host (C64), beim C128 für schnelle Übertragung verwendet.[12] |

| 2 | GND | Masse[11] |

| 3 | /ATN | Serial ATN Ein-/Ausgang. Vom Host auf Masse gezogen beim Begin einer seriellen Datenübertragung.[12] |

| 4 | CLK | Serial CLK Ein-/Ausgang für Bustakt.[12] |

| 5 | DATA | Serial DATA Ein-/Ausgang, serielle (auch schnelle) Datenübertragung.[12] |

| 6 | /RESET | Reset für Peripherie und ältere C64.[12] |

Steuerchip MOS VIA 6522

Erkauft wurde der Preisvorteil des seriellen Busses durch eine stark verringerte Übertragungsgeschwindigkeit im Vergleich zum IEEE-488-Bus. Da sich der verwendete Steuerchip MOS Technology VIA (MOS 6522) kurz vor dem Verkaufsstart des VC 20 als fehlerhaft[13] in der Implementierung seines zum automatischen Senden und Empfangen eines Bytes vorgesehenen Schieberegisters herausstellte, musste diese Aufgabe durch in kürzester Zeit improvisierte und suboptimal programmierte Zugriffsroutinen vom Prozessor mittels Bit-Banging übernommen werden.[14] Hierdurch sank die Übertragungsgeschwindigkeit nochmals um ca. 1/4 ab.[15] Durch den kleinen Speicher des VC 20 und die dementsprechend geringe Größe seiner Programme fiel die niedrige Ladegeschwindigkeit jedoch nicht so stark ins Gewicht. Für damalige Drucker war die Geschwindigkeit ohnehin mehr als ausreichend.

Steuerchip MOS CIA 6526

Obwohl der C64, im Unterschied zum VC 20, die hinsichtlich des implementierten Schieberegisters fehlerfreien CIA-Chips (MOS 6526) verwendete, wurde aus Platzgründen keiner der beiden für die hardware-beschleunigte Variante des seriellen Busses nötigen Pins der CIA-Chips auf der Leiterplatte des C64 an den seriellen Anschluss geführt.[16] Zudem wurde beim C64 aus Gründen der Rückwärtskompatibilität zum VC 20 und dessen Diskettenlaufwerk VC1540, von denen noch wesentliche Lagerbestände vorhanden waren,[17] weiterhin die ursprüngliche Version des Busses verwendet, bei der die Übertragung jedes Bits von den CPUs im C64 und angeschlossenem Diskettenlaufwerk einzeln vorgenommen werden musste. Auch wurden im speziell für den C64 entwickelten Diskettenlaufwerk VC1541 nicht die CIAs, sondern die billigeren, aber fehlerhaften VIAs verbaut.[18] Da beim C64, anders als beim VC 20, der Prozessor vom Videochip VIC II einmal je Textzeile für jeweils mindestens 40 Taktzyklen angehalten wurde,[19] musste die Busgeschwindigkeit im Vergleich zum VC 20 noch einmal abgesenkt werden, damit der C64 während dieses Wartezustands kein Bit vom Diskettenlaufwerk verpasste. Damit stiegen im Zusammenhang mit dem sehr viel größeren Speicher dieses Rechners die Ladezeiten für umfangreiche Programme oftmals auf mehrere Minuten an.

Geschwindigkeit

| Variante | Geschwindigkeit | Effektive Bitrate |

|---|---|---|

| Commodore 64 + 1541 | 300 Byte/s[20] | 2.400 bit/s |

| Commodore 64 + 1541 mit Schnelllader | 2.560 Byte/s[21] | 20.480 bit/s |

| Commodore 128 + 1571 im Burstmodus | 5.200 Byte/s[22] | 41.600 bit/s |

| Theoretischer 20-µs-Takt | 6.250 Byte/s | 50.000 bit/s |

Beschleunigung der Datenübertragung

Es wurden diverse Lösungen zur Beschleunigung der Datenübertragung zwischen dem C64 und einem Diskettenlaufwerk, oftmals mit Hilfe einer abgewandelten Verwendung der Steuerchips CIA und VIA, populär. Diese verwendeten entweder zusätzliche Hardware zusammen mit einem Parallelkabel, das die Leitungen des seriellen CBM-Busses ersetzte, oder zusätzliche Hardware unter Beibehaltung der Leitungen des CBM-Busses. Alternativ kamen reine Softwarelösungen zum Einsatz.[23] Die Modifikationen waren bspw. ein anderes GCR der Daten auf der Diskette[24] und die Verminderung der für die Datenflusssteuerung benötigten Zeit durch die synchrone und parallele Übertragung von ganzen Bitfolgen über die CLK- und DATA-Leitung. Hierbei bestimmte stets der Computer anstatt des sendenden Partners den Beginn der Übertragung, womit sichergestellt wurde, dass die CPU im C64 im Sendefall alle Bits kontinuierlich übertrug und im Empfangsfall keine Bits verpasste.[25]

Die Beschleunigungsroutinen wurden bei den reinen Softwarelösungen zunächst von Diskette mit den Originalroutinen geladen und an geeigneter Stelle im RAM von Computer und Diskettenlaufwerk installiert. Da viele Programme sich nur durch den Reset des Computers beenden ließen, musste dieser Vorgang entsprechend oft wiederholt werden. Der so verursachte Zeitaufwand entfiel allerdings, wenn die Beschleunigungsroutinen in einem ROM in einem am Computer angesteckten Modul oder durch Austausch der Original-ROMs in Computer und Diskettenlaufwerk durch oftmals EPROMs sofort zur Verfügung standen.[23]

Kam zusätzlich noch ein Parallelkabel zum Einsatz, wurde dieses bspw. an einem Ende an den Userport des C64 gesteckt, an seinem anderen Ende befand sich ein angelöteter Chip-Sockel, der zunächst anstatt eines VIA-Chips auf der Leiterplatte des Diskettenlaufwerks VC1541 eingesteckt oder eingelötet wurde. Der zuvor entfernte VIA-Chip wurde nun in diesen Chip-Sockel gesteckt.[26] Zusätzlich musste eine Öffnung in das Laufwerksgehäuse eingearbeitet werden, um dort das Parallelkabel hindurchzuführen. Mit dieser Verbindung wurde ein Parallel-Port des VIA-Chips mit einem Parallel-Port eines CIA-Chips im C64 verbunden, wodurch ein Byte parallel übertragen werden konnte. Diese Lösungen erreichten mit die beste Leistung.

Gängige Hardware-Lösungen waren z. B. SpeedDos (ca. 5- bis 8-fach schnelleres Laden[26]), Dolphindos (ca. 25-fach schnelleres Laden[27]) und JiffyDOS (ca. 10-fach schnelleres Laden[28]).

Der schnelle CBM-Bus am C128

Erst mit dem C128 wurde die lange zuvor geplante hardware-unterstützte Version des seriellen Busses von Commodore realisiert und somit die Busgeschwindigkeit auf einen erträglichen Wert gesteigert. Voraussetzung dafür war die Verwendung der speziell für den C128 entwickelten Diskettenlaufwerke VC1570, VC1571 oder VC1581, da bei diesen ein CIA-Chip mit seinem funktionierenden Schieberegister[29] zum Einsatz kam.

Zur Übertragung eines Bytes mit Hilfe des Schieberegisters wurden stets von einem CIA über Logikchips sein CNT-Pin an die FAST CLK-Leitung (vormals SRQIN-Leitung genannt) und sein SP-Pin an die DATA-Leitung des seriellen Busses geführt.[4][5][30] Mithilfe des jeweiligen SDR-Registers eines CIA[31] konnten nun alle 8 Bits des zu sendenden bzw. empfangenen Bytes gleichzeitig von den CPUs im C128 und angeschlossenem Diskettenlaufwerk dort hineingeschrieben bzw. dort ausgelesen werden, wodurch die Programmschleife zum Senden bzw. Empfangen jedes einzelnen Bits entfallen konnte.[32][33]

Der Burstmodus

Die Diskettenlaufwerke VC1570, VC1571 und VC1581 wiesen zusätzliche Zugriffsroutinen in ihren ROMs als Teil des Burst Command Instruction Set (BCIS) auf. Die darin enthaltene Lese- bzw. Schreibroutine konnte die Daten für eine ganze Gruppe von Diskettensektoren an einem Stück, daher der Name Burstmodus, über den schnellen seriellen CBM-Bus senden bzw. empfangen. Hierbei invertierte der Empfänger zur Bestätigung eines empfangenen Bytes nur noch die CLK-Leitung. Eine Statusüberprüfung während einer solchen Datenübertragung seitens des C128 erfolgte auch nur noch je Diskettensektor.[34]

Da im ROM des C128 die das Gegenstück bildenden Übertragungsroutinen nicht vorhanden waren, mussten diese in dessen RAM geladen und ausgeführt werden. Wurde ein C64 so modifiziert, dass der CNT- und der SP-Pin eines seiner CIA-Chips schlussendlich passend an seinen seriellen Anschluss geführt wurden, konnte er ebenfalls den Burstmodus nutzen.[35]

Über das BCIS war es möglich, auf Disketten zuzugreifen, die die MFM oder das CBM-GCR verwendeten. Insbes. war ein Zugriff auf PC-Disketten möglich.[35] Diskettensektoren konnten mit dem BCIS auch ohne Verwendung des Burstmodus bspw. mit Hilfe des CBM-BASIC gelesen und geschrieben werden.[36]

Weblinks

Einzelnachweise

- ↑ a b c d A. Finkel, N. Harris, P. Higginbottom, M. Tomczyk: VIC 20 Programmer's Reference Guide. Hrsg.: Commodore Business Machines, Inc. and Howard W. Sams & Co., Inc. THE SERIAL BUS (englisch).

- ↑ Commodore Business Machines, Inc. and Howard W. Sams & Co., Inc. (Hrsg.): COMMODORE 64 PROGRAMMER'S REFERENCE GUIDE. Figure 6-4. Serial (englisch).

- ↑ Commodore Electronics Limited: 1571 Disk Drive User's Guide. APPENDIX F SERIAL INTERFACE INFORMATION (englisch).

- ↑ a b 1571 PCB assembly #310420 schematic diagram. (GIF; 662 KB) Abgerufen am 20. Februar 2021 (englisch).

- ↑ a b PCB ASSEMBLY #250471. (GIF; 179 KB) Abgerufen am 20. Februar 2021 (englisch).

- ↑ Michael G. Peltier: 1541 Single Drive Floppy Disk MAINTENANCE MANUAL. 1984, Figure 2-12. Computer, Schematic. (englisch).

- ↑ Jim Butterfield: How the VIC/64 Serial Bus Works. In: COMPUTE! Band 5, Nr. 7, Juli 1983 (englisch): “There are fewer "handshake" lines than on IEEE, and the speed is slower; but the principle is the same.”

- ↑ a b Sheldon Leemon: MAPPING THE Commodore 64. COMPUTE! Publications, Inc., 1984, S. 224 (englisch): “CIOUT; UNTLK; UNLSN; ACPTR”

- ↑ a b Commodore Business Machines, Inc. and Howard W. Sams & Co., Inc. (Hrsg.): COMMODORE 64 PROGRAMMER'S REFERENCE GUIDE. TABLE of OPEN Statement Parameters: (englisch).

- ↑ A. Finkel, N. Harris, P. Higginbottom, M. Tomczyk: VIC 20 Programmer's Reference Guide. Hrsg.: Commodore Business Machines, Inc. and Howard W. Sams & Co., Inc. B-12. Function name: LISTEN; B-31. Function name: TALK (englisch).

- ↑ a b C64 Serial I/O pinout. In: pinouts.ru. 30. Mai 2017. Abgerufen am 15. Februar 2021.

- ↑ a b c d e Serial Bus. MJK's Commodore 64 & LCD Page. 12. Dezember 1997. Abgerufen am 20. Februar 2021.

- ↑ SY6522 Versatile Interface Adapter. (PDF; 5,9 MB) S. 7, abgerufen am 15. Februar 2021 (englisch).

- ↑ Design case history: the Commodore 64 (PDF) 1985. Abgerufen am 17. Februar 2021: „... the 6502 processor sends out one bit at a time under direct software control ...“

- ↑ Brian Bagnall: Commodore. Variant Press (englisch): “... the only way for him to make the disk drive work was to slow down the transfer speed by four times.”

- ↑ Brian Bagnall: Commodore. Variant Press (englisch): “... it was the production engineers in California who cut it off.”

- ↑ Brian Bagnall: Commodore. Variant Press (englisch): “They had inventory on the shelf, ...”

- ↑ Brian Bagnall: Commodore. Variant Press (englisch): “The 1541 became just a 1540 with minor software changes.”

- ↑ Design case history: the Commodore 64 (PDF) 1985. Abgerufen am 17. Februar 2021: „... because the processor in the C-64 is turned off for 40 microseconds every 512 microseconds, ...“

- ↑ Karsten Schramm: Warum ist die 1541 so langsam? In: 64'er. Markt&Technik, Mai 1987.

- ↑ Design case history: the Commodore 64 (PDF) 1985. Abgerufen am 2. April 2016: „Programming tricks used by Epyx have yielded transfer rates of up to 2.5 kilobytes per second.“

- ↑ Commodore 1571 disk drive specifications. Commodore Business Machines, Inc.. Abgerufen am 27. April 2016.

- ↑ a b Hans-Jürgen Humbert: Beschleunigung tut not. In: 64'er. Markt&Technik, November 1992.

- ↑ Martin Pfost: Heureka - es funktioniert! In: 64'er. Markt&Technik, März 1987.

- ↑ JiffySoft 128. H2Obsession, abgerufen am 26. Februar 2021 (englisch).

- ↑ a b TURBO-FLOPPYS - ZWEITE GENERATION. In: 64'er. Markt&Technik, Oktober 1985.

- ↑ Boris Schneider: Schnelle Floppy für wenig Geld. In: 64'er. Markt&Technik, Mai 1986.

- ↑ JiffyDOS User’s Manual. Creative Micro Designs, Inc., S. 8, abgerufen am 27. Februar 2021 (englisch).

- ↑ Design case history: the Commodore 64 (PDF) 1985. Abgerufen am 20. Februar 2021: „We fixed the serial-shift register for the 6526 ...“

- ↑ I/O - Control Ports, Keyboard, User Port, Serial Port, Cassette Port SC SCHEMATIC 310378. (GIF; 131 KB) Abgerufen am 20. Februar 2021 (englisch).

- ↑ 6526 Complex Interface Adapter (CIA). (PDF; 85 KB) Abgerufen am 20. Februar 2021 (englisch): „Serial Port (SDR)“

- ↑ Karsten Schramm: Die Floppy 1570/1571. Markt & Technik Verlag AG, 81ea Routine zum Senden von Daten auf den Bus als Folge eines TALK-Kommandos vom Computer. Die analoge Routine dazu befindet sih [sic] bei $e909 und steuert diesen Betrieb für den 1541-Modus.

- ↑ Karsten Schramm: Die Floppy 1570/1571. Markt & Technik Verlag AG, 82c7 Routine holt ein Datenbyte vom schnellen Bus der 1571 als Folge eines LISTEN-Kommandos vom Computer. Analog dazu ist die Routine bei $e9c9 im DOS.

- ↑ Commodore Electronics Limited (Hrsg.): DISK DRIVE 1570/71 User's Guide. August 1985, CHAPTER 10 BURST COMMANDS (englisch).

- ↑ a b André Fachard: BDOS - Ihr Computer wird zum PC. In: 64'er. Markt&Technik, Juni 1989.

- ↑ Burst Mode and BASIC. Herne Data Systems Ltd., abgerufen am 4. März 2021 (englisch).