Tensor Processing Unit

Tensor Processing Units (TPUs), auch Tensor-Prozessoren, sind anwendungsspezifische Chips um Anwendungen im Rahmen von maschinellem Lernen zu beschleunigen. TPUs werden vor allem genutzt, um Daten in künstlichen neuronalen Netzen, vgl. Deep Learning, zu verarbeiten.

Die von Google entwickelten TPUs wurden speziell für die Softwaresammlung TensorFlow[1] entworfen. TPUs sind die Basis für alle Google Services, welche maschinelles Lernen einsetzen, und wurden auch in den AlphaGo-Maschine-vs.-Mensch-Wettkämpfen mit einem der weltbesten Go-Spieler, Lee Sedol, zum Einsatz gebracht.[2]

Erste Generation

Die erste Generation von Googles TPU wurde auf der Google I/O 2016 vorgestellt und speziell entworfen, um die Anwendung eines bereits trainierten künstlichen neuronalen Netzwerks zu unterstützen bzw. zu beschleunigen.[3] Dies wurde u. a. durch eine geringere Präzision im Vergleich zu normalen CPUs oder GPUs und einer Spezialisierung auf Matrizenoperationen erreicht.

Die TPU besteht aus einem systolischen Array mit einer 256×256 8-Bit-Matrizenmultiplikationseinheit (MMU), welche von einem Mikroprozessor mit einem CISC-Befehlsatz angesteuert wird. Der Chip wurde in einem 28-nm-Prozess gefertigt und taktet mit 700 MHz bei einer TDP von 28 bis 40 W. Die TPU besitzt 28 MiB Arbeitsspeicher am Chip. Zudem sind 4-MiB-32-Bit-Akkumulatoren verbaut, welche die Ergebnisse der Matrizenmultiplikationseinheit übernehmen. Die TPU kann Matrizenmultiplikationen, Faltungen und Aktivierungsfunktionen, sowie Datentransfer zum Hostsystem über PCIe 3.0 oder zum DDR3 DRAM, welcher sich am Board befindet, ausführen.

Zweite Generation

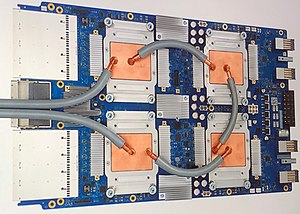

Die zweite Generation von Googles TPU (TPUv2) wurde auf der Google I/O 2017 vorgestellt. Diese soll nicht nur die Anwendung von neuronalen Netzwerken (Inferenz), sondern auch das Training dieser Netzwerke beschleunigen. Diese TPUs besitzen zwei „Matrizenausführungseinheiten“ (

; MXU) mit je 8 GiB Arbeitsspeicher.[4] Jede MXU weist eine Rechenleistung von 22,5 TFLOPS auf, wobei jedoch der bfloat16-Datentyp zum Einsatz kommt, welcher nicht IEEE 754 entspricht.[4] Ein TPU-Board mit 4 TPUs kommt somit auf 180 TFLOPS.

Die TPUs werden zu einem „Pod“ mit 11,5 PFLOPS zusammengeschaltet, einem Rechnerverbund (Cluster-Systemarchitektur) von 256 TPUs und 128 Server-CPUs. Die TPUs sind hierbei in einer sphärenförmigen (2D-Torus) Netzwerktopologie von je 8×8 TPUs zusammengeschaltet. Zur Verbindung der CPUs mit den TPUs kommt PCI-Express 3.0 mit 32 Lanes (8 Lanes je TPU) zum Einsatz.[4]

Die TPUs der zweiten Generation sind in Form der Google Compute Engine, einem Cloud-Angebot von Google, nutzbar.

Um die Speicherbandbreite der Architektur zu erhöhen kommt HBM-Speicher zum Einsatz.[5]

Die Chipfläche dürfte bei der zweiten Generation aufgrund des aufwändigeren Speicherinterface und der 2 Cores pro Chip größer ausfallen als die der ersten Generation.

Dritte Generation

Die dritte Generation von Googles TPU (TPU 3.0) wurde auf der Google I/O 2018 vorgestellt. Die TPUs besitzen 4 MXUs mit je 8 GiB Arbeitsspeicher (32 GiB je TPU).[4] Die Netzwerktopologie der TPUs ist ebenfalls in Form eines 2D-Torus ausgelegt. Die Racks besitzen zudem eine Wasserkühlung, mit der die TPUs gekühlt werden.[4] TPU 3.0-Pods bestehen aus 8 Racks mit insgesamt 1024 TPUs und 256 Server-CPUs. Die Rechenleistung eines Pod liegt bei knapp über 100 PFLOPS.[4]

Vierte Generation

Die vierte Generation von Googles TPU (TPU v4) wurde von Google im Dezember 2021 vorgestellt.[6]

Literatur

- Norman P. Jouppi, Cliff Young, Nishant Patil, David Patterson: A domain-specific architecture for deep neural networks. In: Communications of the ACM. 61, 2018, S. 50, doi:10.1145/3154484.

Weblinks

- Cloud TPUs (TensorFlow @ O’Reilly AI Conference, San Francisco '18) auf YouTube, vom 25. Oktober 2018

- A simple classification model using Keras with Cloud TPUs. In: colab.research.google.com. Abgerufen am 10. November 2018.

- Edge TPU Devices. In: aiyprojects.withgoogle.com. Abgerufen am 22. März 2019.

- Sebastian Grüner: Tensor Processing Unit: Google baut eigene Chips für maschinelles Lernen. In: golem.de. 19. Mai 2016, abgerufen am 23. November 2016.

- Harald Bögeholz: Künstliche Intelligenz: Architektur und Performance von Googles KI-Chip TPU – heise online. In: heise.de. 6. April 2017, abgerufen am 7. April 2017.

- David Patterson, Google TPU Team: In-Data Center Performance Analysis of a Tensor Processing Unit. (PDF) 2. April 2017, abgerufen am 23. Mai 2017 (englisch).

Patente

- Patent US20160342889: Vector Computation Unit in Neural Network Processor. Angemeldet am 3. September 2015, veröffentlicht am 24. November 2016, Anmelder: Google Inc., Erfinder: Gregory Michael Thorson, Christopher Aaron Clark, Dan Luu.

- Patent WO2016186823: Batch Processing in a Neural Network Processor. Angemeldet am 3. März 2016, veröffentlicht am 24. November 2016, Anmelder: Google Inc., Erfinder: Reginald Clifford Young.

- Patent WO2016186801: Neural Network Processor. Angemeldet am 26. April 2016, veröffentlicht am 24. November 2016, Anmelder: Google Inc., Erfinder: Jonathan Ross, Norman Paul Jouppi, Andrew Everett Phelps, Reginald Clifford Young, Thomas Norrie, Gregory Michael Thorson, Dan Luu.

- Patent WO2014105865: System and method for parallelizing convolutional neural networks. Angemeldet am 23. Dezember 2013, veröffentlicht am 3. Juli 2014, Anmelder: Google Inc., Erfinder: Alexander Krizhevsky, Ilya Sutskever, Geoffrey E. Hinton.

Einzelnachweise

- ↑ Jeff Dean, Rajat Monga: TensorFlow - Google’s latest machine learning system, open sourced for everyone. In: Google Research Blog. Google, 9. November 2015, abgerufen am 29. Juni 2016 (englisch).

- ↑ Christof Windeck: Google I/O 2016: "Tensor-Prozessoren" halfen beim Go-Sieg – heise online. In: heise.de. 19. Mai 2016, abgerufen am 23. November 2016.

- ↑ Norm Jouppi: Google supercharges machine learning tasks with TPU custom chip. In: Google Cloud Platform Blog. 18. Mai 2016, abgerufen am 29. Juni 2016 (amerikanisches Englisch).

- ↑ a b c d e f Timothy Prickett Morgan: Tearing apart Google's TPU 3.0 AI Coprocessor. In: The Next Platform. 10. Mai 2018, abgerufen am 24. Mai 2018 (englisch).

- ↑ Systemarchitektur | Cloud TPU. Abgerufen am 12. Januar 2020.

- ↑ Google showcases Cloud TPU v4 Pods for large model training |. Abgerufen am 11. April 2022.